# DE1-SoC Computer System with ARM\* Cortex\* A9

For Ouartus® Prime 17.1

#### 1 Introduction

This document describes a computer system that can be implemented on the Intel<sup>®</sup> DE1-SoC development and education board. This system, called the *DE1-SoC Computer*, is intended for use in experiments on computer organization and embedded systems.

### 2 DE1-SoC Computer Contents

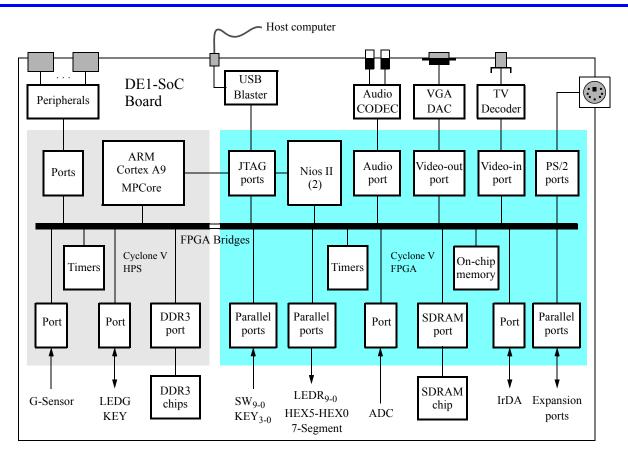

A block diagram of the DE1-SoC Computer system is shown in Figure 1. As indicated in the figure, the components in this system are implemented utilizing the *Hard Processor System* (HPS) and FPGA inside the Cyclone<sup>®</sup> V SoC chip. The HPS comprises an ARM\* Cortex\* A9 dual-core processor, a DDR3 memory port, and a set of peripheral devices. The FPGA implements two Intel Nios<sup>®</sup> II processors, and several peripheral ports: memory, timer modules, audio-in/out, video-in/out, PS/2, analog-to-digital, infrared receive/transmit, and parallel ports connected to switches and lights. Instructions for using the Nios II processors are provided in a separate document, called *DE1-SoC Computer System with Nios II*.

#### 2.1 Hard Processor System

The hard processor system (HPS), as shown in Figure 1, includes an ARM Cortex A9 dual-core processor. The A9 dual-core processor features two 32-bit CPUs and associated subsystems that are implemented as hardware circuits in the Intel Cyclone V SoC chip. An overview of the ARM A9 processor can be found in the document *Introduction to the ARM Processor*, which is provided in Intel's FPGA University Program web site. All of the I/O peripherals in the DE1-SoC Computer are accessible by the processor as memory mapped devices, using the address ranges that are given in this document. A summary of the address map can be found in Section 7.

A good way to begin working with the DE1-SoC Computer and the ARM A9 processor is to make use of a utility called the *Intel*<sup>®</sup> *FPGA Monitor Program*. It provides an easy way to assemble/compile ARM A9 programs written in either assembly language or the C language. The Monitor Program, which can be downloaded from Intel's web site, is an application program that runs on the host computer connected to the DE1-SoC board. The Monitor Program can be used to control the execution of code on the ARM A9, list (and edit) the contents of processor registers, display/edit the contents of memory on the DE1-SoC board, and similar operations. The Monitor Program includes the DE1-SoC Computer as a pre-designed system that can be downloaded onto the DE1-SoC board, as well as several sample programs in assembly language and C that show how to use the DE1-SoC Computer's peripherals. Section 8 describes how the DE1-SoC Computer is integrated with the Monitor Program. An overview of the Monitor Program is available in the document *Intel*<sup>®</sup> *FPGA Monitor Program Tutorial*, which is provided in the University Program web site.

Figure 1. Block diagram of the DE1-SoC Computer.

#### 2.2 Memory

The HPS includes a memory port that connects the ARM MPCORE\* to a 1 GB DDR3 memory. This memory is normally used as the storage location of programs and data used by the ARM processors. The memory is organized as 256M x 32-bits, and is accessible using word accesses (32 bits), halfwords, and bytes. The DDR3 memory is mapped to the address space 0x00000000 to 0x3FFFFFF. There is also a 64 KB on-chip memory available inside each ARM A9 processor. This small memory is organized as 16K x 32-bits, and is mapped to the address space 0xFFFF0000 to 0xFFFFFFFF.

#### 2.3 Pushbutton KEY and LED Port

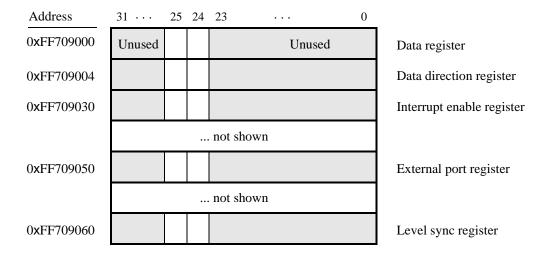

The HPS includes a general purpose I/O port, called *GPIO1*, that is accessible by the ARM A9 processor. As illustrated in Figure 2, this parallel port is assigned the *Base* address 0xFF709000, and includes several 32-bit registers. These registers can be read or written using word accesses. Only two bit locations in GPIO1 are used for the DE1-SoC Computer. Bit 24 of the data register (DR) is connected to a green light, LEDG, and bit 25 is connected to a pushbutton switch, KEY. To use these devices, the *data direction register* (DDR) shown in the figure has to be configured such that bit 24 is an output and bit 25 is an input. Writing a 1 into a corresponding bit position in the

DDR sets this bit as an output, while writing a 0 sets the bit as an input. After the direction bits have been set, the green light LEDG can be turned on/off by writing to bit 24 in the data register. The value of the pushbutton switch KEY can be obtained by reading the external port register and checking the value of bit 25. An example program for the ARM A9 processor that uses GPIO1 is given in Section 2.4.

As indicated in Figure 2, the GPIO1 port includes several other registers in addition to the DR and DDR registers. These other registers are mostly used for setting characteristics of input pins, which affects only the KEY input in our system. Detailed information about these registers can be found in the *Intel Cyclone V Hard Processor System* documentation, which is available on Intel's website.

Figure 2. Parallel port GPIO1.

#### 2.4 Timer Modules

The HPS includes several hardware timer modules that can be used to keep track of time intervals. The ARM A9 MPCore includes one *private* timer module for each A9 core, and the HPS provides four other timer modules that can be used by either A9 core. The timers are described in more detail below.

#### 2.4.1 ARM\* A9\* MPCore\* Timers

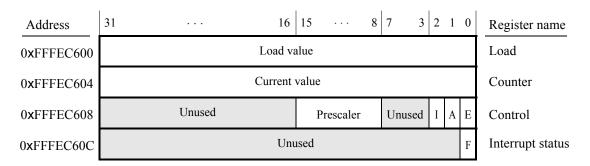

Figure 3 shows the registers in the programmer's interface for each A9 core private timer. These registers have the base address 0xFFFEC600, as shown in the figure, and can be read or written using word accesses. To use the timer, it is necessary to first write an initial count value into the *Load* register. The timer can then be started by setting the enable bit *E* in the *Control* register to 1, and it can be stopped by setting *E* back to 0. Once enabled the timer decrements its count value until reaching 0. When it reaches 0, the timer sets the *F* bit in the *Interrupt status* register. The *F* bit can be checked by software using polled-I/O to determine when the timer period has expired. The *F* bit can be reset to 0 by writing a 1 into it. Also, if bit *I* in the *Control* register is set to 1, then a processor interrupt can be generated when the timer reaches 0. Using interrupts with the timer is discussed in Section 3.

When it reaches 0, the timer will stop if the auto bit (A) in the control register is set to 0. But if bit A is set to 1, then the timer will automatically reload the value in the *Load* register and continue decrementing. The current value of the timer is available to software in the *Counter* register shown in Figure 3. The timer uses a clock frequency of 200 MHz. The *Prescaler* field in the *Control* register can be used to slow down the counting rate, as follows. The timer decrements each *Prescaler* +1 clock cycle. Therefore, if *Prescaler* = 0, then the timer decrements every clock cycle, if *Prescaler* = 1, the timer decrements every second clock cycle, and so on.

Figure 3. ARM A9 private timer port.

#### 2.4.2 HPS Timers

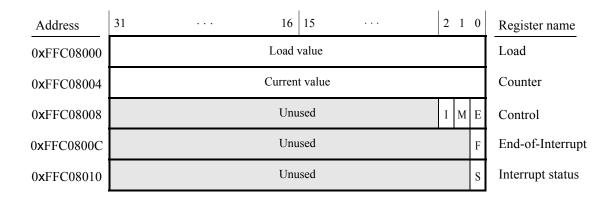

Figure 4 shows the registers in the programmer's interface for one of the HPS timers. These registers have the base address 0xFFC08000, as shown in the figure, and can be read or written using word accesses. To configure the timer, it is necessary to ensure that it is stopped by setting the enable bit E in the Control register to 0. A starting count value for the timer can then be written into the Load register. To instruct the timer to use the specified starting count value, the E in the

The current value of the timer is available to software in the *Counter* register shown in Figure 4. The timer uses a clock frequency of 100 MHz.

There are three other identical timers in the HPS, with the following base addresses: 0xFFC09000, 0xFFD00000, and 0xFFD01000. The first of these timers uses a 100 MHz clock, and the last two timers use a 25 MHz clock.

We should mention that other timer modules also exist in the HPS. The ARM A9 MPCore has a *global* timer that is shared by both A9 cores, as well as a *watchdog* timer for each processor. Also, the HPS has two additional watchdog timers. Documentation about the global timer and watchdog timers is available in the *ARM Cortex A9 MPCore Technical Reference Manual*, and in the *Intel Cyclone V Hard Processor System Technical Reference Manual*.

Figure 4. HPS timer port.

#### 2.4.3 Using a Timer with Assembly Language Code

An example of ARM A9 assembly language code is included in the Appendix in Listing 1. The code configures the private timer for the A9 core so that it produces one-second timeouts. An infinite loop is used to flash the green light connected to GPIO1, discussed in Section 2.3. The light is turned on for one second, then off, and so on.

An example of C code is also included in Listing 2. This code performs the same actions as the assembly language program in Listing 1—it flashes on/off the green light connected to GPIO1 at one-second intervals.

The source code files shown in Listings 2 and 1 are distributed as part of the Intel<sup>®</sup> FPGA Monitor Program. The files can be found under the heading *sample programs*, and are identified by the name *Timer Lights*.

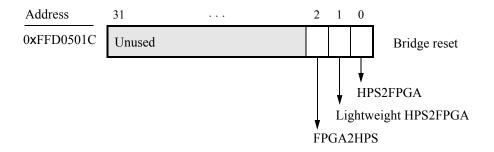

#### 2.5 FPGA Bridges

The FPGA bridges depicted in Figure 1 provide connections between the HPS and FPGA in the Cyclone V SoC device. The bridges are enabled, or disabled, by using the Bridge reset register, which is illustrated in Figure 5 and has the address 0xFFD0501C. Three distinct bridges exist, called HPS-to-FPGA, lightweight HPS-to-FPGA, and FPGA-to-HPS. In the DE1-SoC Computer the first two of these bridges are used to connect the ARM A9 processor to the FPGA. As indicated in Figure 5 the bridges are enabled/disabled by bits 0 – 2 of the Bridge reset register. To use the memory-mapped peripherals in the FPGA, software running on the ARM A9 must enable the HPS-to-FPGA and lightweight HPS-to-FPGA bridges by setting bits #0 and #1 of the Bridge reset register to 0. We should note that if a user program is downloaded and run on the ARM A9 by using the Intel<sup>®</sup> FPGA Monitor Program, described in Section 8, then these bridges are automatically enabled before the user program is started.

In addition to the components described above, the HPS also provides a number of other peripheral devices, such as USB, Ethernet, and a 3-D accelerometer (G-sensor). The G-sensor is described in the tutorial *Using the DE1-SoC Accelerometer with ARM*, available from Intel's FPGA University Program website. Documentation about the other devices connected to the HPS can be found in the *Intel Cyclone V Hard Processor System Technical Reference Manual*, as well as in the *DE1-SoC Board User Manual*.

Figure 5. FPGA bridge reset register.

#### 2.6 FPGA Components

As shown in Figure 1 a number of components in the DE1-SoC Computer are implemented inside the FPGA in the Cyclone<sup>®</sup> V SoC chip. Several of these components are described in this section, and the others are presented in Section 4.

#### 2.7 Nios® II Processor

The Intel Nios II processor is a 32-bit CPU that can be implemented in an Intel FPGA device. Two versions of the Nios II processor are available, designated economy (/e) and fast (/f). The DE1-SoC Computer includes two instances of the Nios II/f version, configured with floating-point hardware support. Instructions for using the Nios II processors in the DE1-SoC Computer are provided in a separate document, called *DE1-SoC Computer with Nios II*.

#### 2.8 Memory Components

The DE1-SoC Computer has an SDRAM port, as well as two memory modules implemented using the on-chip memory inside the FPGA. These memories are described below.

#### 2.8.1 SDRAM

An SDRAM Controller in the FPGA provides an interface to the 64 MB synchronous dynamic RAM (SDRAM) on the DE1-SoC board, which is organized as 32M x 16 bits. It is accessible by the ARM A9 processor using word (32-bit), halfword (16-bit), or byte operations, and is mapped to the address space 0xC0000000 to 0xC3FFFFFF.

#### 2.8.2 On-Chip Memory

The DE1-SoC Computer includes a 256 KB memory that is implemented inside the FPGA. This memory is organized as 64K x 32 bits, and spans addresses in the range 0xC8000000 to 0xC803FFF. The memory is used as a pixel buffer for the video-out and video-in ports.

#### 2.8.3 On-Chip Memory Character Buffer

The DE1-SoC Computer includes an 8 KB memory implemented inside the FPGA that is used as a character buffer for the video-out port, which is described in Section 4.2. The character buffer memory is organized as 8K x 8 bits, and spans the address range 0xC9000000 to 0xC9001FFF.

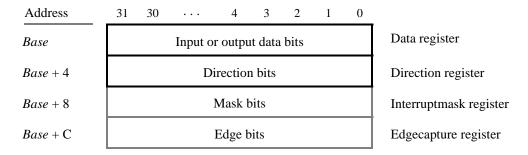

#### 2.9 Parallel Ports

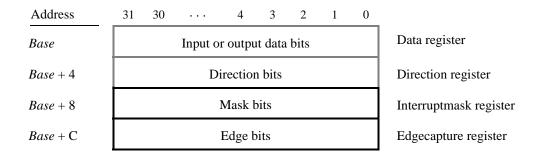

There are several parallel ports implemented in the FPGA that support input, output, and bidirectional transfers of data between the ARM A9 processor and I/O peripherals. As illustrated in Figure 6, each parallel port is assigned a *Base* address and contains up to four 32-bit registers. Ports that have output capability include a writable *Data* register, and ports with input capability have a readable *Data* register. Bidirectional parallel ports also include a *Direction* register that has the same bit-width as the *Data* register. Each bit in the *Data* register can be configured as an input by setting the corresponding bit in the *Direction* register to 0, or as an output by setting this bit position to 1. The *Direction* register is assigned the address *Base* + 4.

Figure 6. Parallel port registers in the DE1-SoC Computer.

Some of the parallel ports in the DE1-SoC Computer have registers at addresses *Base* + 8 and *Base* + C, as indicated in Figure 6. These registers are discussed in Section 3.

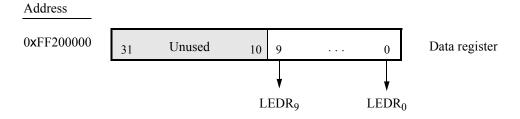

#### 2.9.1 Red LED Parallel Port

The red lights  $LEDR_{9-0}$  on the DE1-SoC board are driven by an output parallel port, as illustrated in Figure 7. The port contains a 10-bit Data register, which has the address 0xFF200000. This register can be written or read by the processor using word accesses, and the upper bits not used in the registers are ignored.

Figure 7. Output parallel port for *LEDR*.

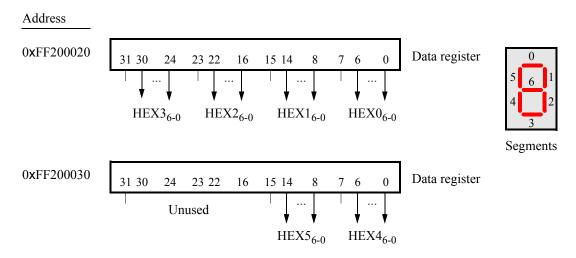

#### 2.9.2 7-Segment Displays Parallel Port

There are two parallel ports connected to the 7-segment displays on the DE1-SoC board, each of which comprises a 32-bit write-only *Data* register. As indicated in Figure 8, the register at address 0xFF200020 drives digits *HEX3* to *HEX0*, and the register at address 0xFF200030 drives digits *HEX5* and *HEX4*. Data can be written into these two registers, and read back, by using word operations. This data directly controls the segments of each display, according to the bit locations given in Figure 8. The locations of segments 6 to 0 in each seven-segment display on the DE1-SoC board is illustrated on the right side of the figure.

Figure 8. Bit locations for the 7-segment displays parallel ports.

#### 2.9.3 Slider Switch Parallel Port

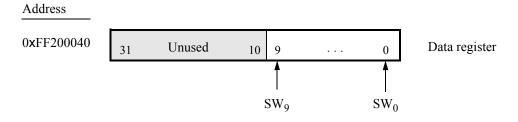

The  $SW_{9-0}$  slider switches on the DE1-SoC board are connected to an input parallel port. As illustrated in Figure 9, this port comprises a 10-bit read-only *Data* register, which is mapped to address 0xFF200040.

Figure 9. *Data* register in the slider switch parallel port.

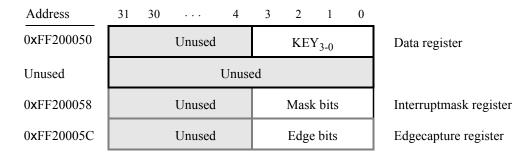

#### 2.9.4 Pushbutton Key Parallel Port

The parallel port connected to the  $KEY_{3-0}$  pushbutton switches on the DE1-SoC board comprises three 4-bit registers, as shown in Figure 10. These registers have the base address 0xFF200050 and can be accessed using word operations. The read-only *Data* register provides the values of the switches  $KEY_{3-0}$ . The other two registers shown

Address 30 0 31 4 3 2 0xFF200050 Unused KEY<sub>3-0</sub> Data register Unused Unused 0xFF200058 Unused Mask bits Interruptmask register 0xFF20005C Unused Edge bits Edgecapture register

in Figure 10, at addresses 0xFF200058 and 0xFF20005C, are discussed in Section 3.

Figure 10. Registers used in the pushbutton parallel port.

#### 2.9.5 Expansion Parallel Port

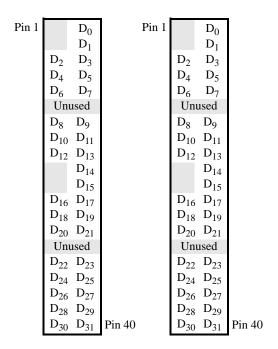

The DE1-SoC Computer includes two bidirectional parallel ports that are connected to the JP1 and JP2 40-pin headers on the DE1-SoC board. These parallel ports include the four 32-bit registers that were described previously for Figure 6. The base address of the port for JP1 is 0xFF200060, and for JP2 is 0xFF200070. Figure 11 gives a diagram of the 40-pin connectors on the DE1-SoC board, and shows how the respective parallel port Data register bits,  $D_{31-0}$ , are assigned to the pins on the connector. The figure shows that bit  $D_0$  of the parallel port is assigned to the pin at the top right corner of the connector, bit  $D_1$  is assigned below this, and so on. Note that some of the pins on the 40-pin header are not usable as input/output connections, and are therefore not used by the parallel ports. Also, only 32 of the 36 data pins that appear on each connector can be used.

#### 2.9.6 Using the Parallel Ports with Assembly Language Code and C Code

The DE1-SoC Computer provides a convenient platform for experimenting with ARM A9 assembly language code, or C code. A simple example of such code is provided in the Appendix in Listings 3 and 4. Both programs perform the same operations, and illustrate the use of parallel ports by using either assembly language or C code.

The code in the figures displays the values of the SW switches on the LED lights. A rotating pattern is displayed on the LEDs. This pattern is rotated to the left by using an ARM A9 *rotate* instruction, and a delay loop is used to make the shifting slow enough to observe. The pattern can be changed to the values of the SW switches by pressing a pushbutton KEY. When a pushbutton key is pressed, the program waits in a loop until the key is released.

The source code files shown in Listings 3 and 4 are distributed as part of the Intel<sup>®</sup> FPGA Monitor Program. The files can be found under the heading *sample programs*, and are identified by the name *Getting Started*.

#### 2.10 JTAG\* Port

The JTAG\* port implements a communication link between the DE1-SoC board and its host computer. This link can be used by the Intel Quartus<sup>®</sup> Prime software to transfer FPGA programming files into the DE1-SoC board, and by the Intel<sup>®</sup> FPGA Monitor Program, discussed in Section 8. The JTAG port also includes a UART, which can be used

Figure 11. Assignment of parallel port bits to pins on JP1 and JP2.

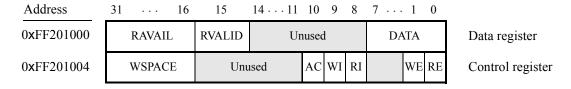

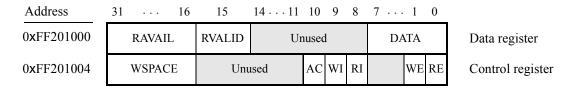

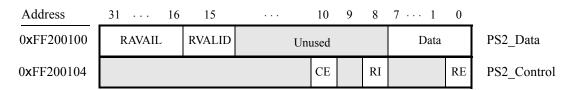

to transfer character data between the host computer and programs that are executing on the ARM A9 processor. If the Intel<sup>®</sup> FPGA Monitor Program is used on the host computer, then this character data is sent and received through its *Terminal Window*. The programming interface of the JTAG UART consists of two 32-bit registers, as shown in Figure 12. The register mapped to address 0xFF201000 is called the *Data* register and the register mapped to address 0xFF201004 is called the *Control* register.

Figure 12. JTAG UART registers.

When character data from the host computer is received by the JTAG UART it is stored in a 64-character FIFO. The number of characters currently stored in this FIFO is indicated in the field RAVAIL, which are bits 31-16 of the Data register. If the receive FIFO overflows, then additional data is lost. When data is present in the receive FIFO, then the value of RAVAIL will be greater than 0 and the value of bit 15, RVALID, will be 1. Reading the character at the head of the FIFO, which is provided in bits 7-0, decrements the value of RAVAIL by one and returns this decremented value as part of the read operation. If no data is present in the receive FIFO, then RVALID will be set to 0 and the data in bits 7-0 is undefined.

The JTAG UART also includes a 64-character FIFO that stores data waiting to be transmitted to the host computer. Character data is loaded into this FIFO by performing a write to bits 7–0 of the *Data* register in Figure 12. Note that writing into this register has no effect on received data. The amount of space, *WSPACE*, currently available in the transmit FIFO is provided in bits 31–16 of the *Control* register. If the transmit FIFO is full, then any characters written to the *Data* register will be lost.

Bit 10 in the *Control* register, called *AC*, has the value 1 if the JTAG UART has been accessed by the host computer. This bit can be used to check if a working connection to the host computer has been established. The *AC* bit can be cleared to 0 by writing a 1 into it.

The Control register bits RE, WE, RI, and WI are described in Section 3.

#### 2.10.1 Using the JTAG\* UART with Assembly Language Code and C Code

Listings 5 and 6 give simple examples of assembly language and C code, respectively, that use the JTAG UART. Both versions of the code perform the same function, which is to first send an ASCII string to the JTAG UART, and then enter an endless loop. In the loop, the code reads character data that has been received by the JTAG UART, and echoes this data back to the UART for transmission. If the program is executed by using the Intel<sup>®</sup> FPGA Monitor Program, then any keyboard character that is typed into the *Terminal Window* of the Monitor Program will be echoed back, causing the character to appear in the *Terminal Window*.

The source code files shown in Listings 5 and 6 are made available as part of the Intel<sup>®</sup> FPGA Monitor Program. The files can be found under the heading *sample programs*, and are identified by the name *JTAG UART*.

#### 2.10.2 Second JTAG\* UART

The DE1-SoC Computer includes a second JTAG UART that is accessible by the ARM A9 MPCORE. This second UART is mapped to the base address 0xFF201008, and operates as described above. The reason that two JTAG UARTs are provided is to allow each processor in the ARM A9 MPCORE to have access to a separate UART.

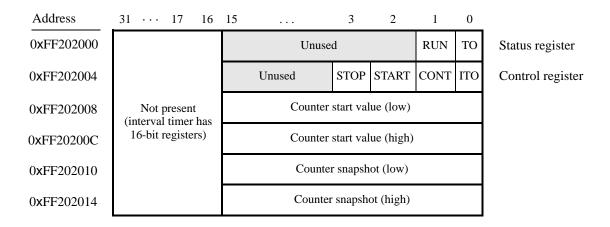

#### 2.11 Interval Timers

The DE1-SoC Computer includes a timer module implemented in the FPGA that can be used by the ARM A9 processor. This timer can be loaded with a preset value, and then counts down to zero using a 100-MHz clock. The programming interface for the timer includes six 16-bit registers, as illustrated in Figure 13. The 16-bit register at address 0xFF202000 provides status information about the timer, and the register at address 0xFF202004 allows control settings to be made. The bit fields in these registers are described below:

- TO provides a timeout signal which is set to 1 by the timer when it has reached a count value of zero. The TO bit can be reset by writing a 0 into it.

- *RUN* is set to 1 by the timer whenever it is currently counting. Write operations to the status halfword do not affect the value of the *RUN* bit.

- ITO is used for generating interrupts, which are discussed in section 3.

Figure 13. Interval timer registers.

- *CONT* affects the continuous operation of the timer. When the timer reaches a count value of zero it automatically reloads the specified starting count value. If *CONT* is set to 1, then the timer will continue counting down automatically. But if *CONT* = 0, then the timer will stop after it has reached a count value of 0.

- (START/STOP) is used to commence/suspend the operation of the timer by writing a 1 into the respective bit.

The two 16-bit registers at addresses 0xFF202008 and 0xFF20200C allow the period of the timer to be changed by setting the starting count value. The default setting provided in the DE1-SoC Computer gives a timer period of 125 msec. To achieve this period, the starting value of the count is  $100 \text{ MHz} \times 125 \text{ msec} = 12.5 \times 10^6$ . It is possible to capture a snapshot of the counter value at any time by performing a write to address 0xFF202010. This write operation causes the current 32-bit counter value to be stored into the two 16-bit timer registers at addresses 0xFF202010 and 0xFF202014. These registers can then be read to obtain the count value.

A second interval timer, which has an identical interface to the one described above, is also available in the FPGA, starting at the base address 0xFF202020.

#### 2.12 System ID

The system ID module provides a unique value that identifies the DE1-SoC Computer system. The host computer connected to the DE1-SoC board can query the system ID module by performing a read operation through the JTAG port. The host computer can then check the value of the returned identifier to confirm that the DE1-SoC Computer has been properly downloaded onto the DE1-SoC board. This process allows debugging tools on the host computer, such as the Intel<sup>®</sup> FPGA Monitor Program, to verify that the DE1-SoC board contains the required computer system before attempting to execute code that has been compiled for this system.

### 3 Exceptions and Interrupts

The A9 processor supports eight types of exceptions, including the *reset* exception and the *interrupt request* (IRQ) exception, as well a number of exceptions related to error conditions. All of the exception types are described in the document *Introduction to the ARM Processor*, which is provided in Intel's FPGA University Program web site. Exception processing uses a table in memory, called the *vector table*. This table comprises eight words in memory and has one entry for each type of exception. The contents of the vector table have to be set up by software, which typically places a branch instruction in each word of the table, where the branch target is the desired exception service routine. When an exception occurs, the A9 processor stops the execution of the program that is currently running, and then fetches the instruction stored at the corresponding vector table entry. The vector table usually starts at the address 0x000000000 in memory. The first entry in the table corresponds to the reset vector, and the IRQ vector uses the seventh entry in the table, at the address 0x00000018.

The IRQ exception allows I/O peripherals to generate interrupts for the A9 processor. All interrupt signals from the peripherals are connected to a module in the processor called the *generic interrupt controller* (GIC). The GIC allows individual interrupts for each peripheral to be either enabled or disabled. When an enabled interrupt happens, the GIC causes an IRQ exception in the A9 processor. Since the same vector table entry is used for all interrupts, the software for the interrupt service routine must determine the source of the interrupt by querying the GIC. Each peripheral is identified in the GIC by an interrupt identification (ID) number. Table 1 gives the assignment of interrupt IDs for each of the I/O peripherals in the DE1-SoC Computer. The rest of this section describes the interrupt behavior associated with the timers and parallel ports.

| A9 Private Timer       29         HPS GPIO1       197         HPS Timer 0       199         HPS Timer 1       200 | I/O Peripheral             | Interrupt ID # |

|-------------------------------------------------------------------------------------------------------------------|----------------------------|----------------|

| HPS Timer 0 199                                                                                                   | A9 Private Timer           | 29             |

|                                                                                                                   | HPS GPIO1                  | 197            |

| HPS Timer 1 200                                                                                                   | HPS Timer 0                | 199            |

| <b> </b>                                                                                                          | HPS Timer 1                | 200            |

| HPS Timer 2 201                                                                                                   | HPS Timer 2                | 201            |

| HPS Timer 3 202                                                                                                   | HPS Timer 3                | 202            |

| FPGA Interval Timer 72                                                                                            | FPGA Interval Timer        | 72             |

| FPGA Pushbutton KEYs 73                                                                                           | FPGA Pushbutton KEYs       | 73             |

| FPGA Second Interval Timer 74                                                                                     | FPGA Second Interval Timer | 74             |

| FPGA Audio 78                                                                                                     | FPGA Audio                 | 78             |

| FPGA PS/2 79                                                                                                      | FPGA PS/2                  | 79             |

| FPGA JTAG 80                                                                                                      | FPGA JTAG                  | 80             |

| FPGA Infrared (IrDA) 81                                                                                           | FPGA Infrared (IrDA)       | 81             |

| FPGA JP1 Expansion 83                                                                                             | FPGA JP1 Expansion         | 83             |

| FPGA JP2 Expansion 84                                                                                             | FPGA JP2 Expansion         | 84             |

| FPGA PS/2 Dual 89                                                                                                 | FPGA PS/2 Dual             | 89             |

Table 1. Interrupt IDs in the DE1-SoC Computer.

#### 3.1 Interrupts from the ARM\* A9\* Private Timer

Figure 3, in Section 2.4.1, shows four registers that are associated with the A9 private timer. As we said in Section 2.4.1, bit *F* in the *Interrupt status* register is set to 1 when the timer reaches a count value of 0. It is possible to generate an A9 interrupt when this occurs, by using bit *I* of the *Control* register. Setting bit *I* to 1 causes the timer to send an interrupt signal to the GIC whenever the timer reaches a count value of 0. The *F* bit can be cleared to 0 by writing writing a 1 into the *Interrupt status* register.

#### 3.2 Interrupts from the HPS Timers

Figure 4, in Section 2.4.2, shows five registers that are associated with each HPS timer. As we said in Section 2.4.2, when the timer reaches a count value of zero, bit *F* in the *End-of-Interrupt* register is set to 1. The value of the *F* bit is also reflected in the *S* bit in the *Interrupt status* register. It is possible to generate an A9 interrupt when the *F* bit becomes 1, by using the *I* bit of the *Control* register. Setting bit *I* to 0 *unmasks* the interrupt signal, and causes the timer to send an interrupt signal to the GIC whenever the *F* bit is 1. After an interrupt occurs, it can be cleared by reading the *End-of-Interrupt* register.

#### 3.3 Interrupts from the FPGA Interval Timer

Figure 13, in Section 2.11, shows six registers that are associated with the interval timer. As we said in Section 2.11, the *TO* bit in the *Status* register is set to 1 when the timer reaches a count value of 0. It is possible to generate an interrupt when this occurs, by using the *ITO* bit in the *Control* register. Setting the *ITO* bit to 1 causes an interrupt request to be sent to the GIC whenever *TO* becomes 1. After an interrupt occurs, it can be cleared by writing any value into the *Status* register.

#### 3.4 Interrupts from Parallel Ports

Parallel ports implemented in the FPGA in the DE1-SoC Computer were illustrated in Figure 6, which is reproduced as Figure 14. As the figure shows, parallel ports that support interrupts include two related registers at the addresses Base + 8 and Base + C. The Interruptmask register, which has the address Base + 8, specifies whether or not an interrupt signal should be sent to the GIC when the data present at an input port changes value. Setting a bit location in this register to 1 allows interrupts to be generated, while setting the bit to 0 prevents interrupts. Finally, the parallel port may contain an Edgecapture register at address Base + C. Each bit in this register has the value 1 if the corresponding bit location in the parallel port has changed its value from 0 to 1 since it was last read. Performing a write operation to the Edgecapture register sets all bits in the register to 0, and clears any associated interrupts.

#### 3.4.1 Interrupts from the Pushbutton Keys

Figure 10, reproduced as Figure 15, shows the registers associated with the pushbutton parallel port. The *Interrupt-mask* register allows interrupts to be generated when a key is pressed. Each bit in the *Edgecapture* register is set to 1 by the parallel port when the corresponding key is pressed. An interrupt service routine can read this register to determine which key has been pressed. Writing any value to the *Edgecapture* register deasserts the interrupt signal being sent to the GIC and sets all bits of the *Edgecapture* register to zero.

Figure 14. Registers used for interrupts from the parallel ports.

Figure 15. Registers used for interrupts from the pushbutton parallel port.

#### 3.5 Interrupts from the JTAG\* UART

Figure 12, reproduced as Figure 16, shows the data and *Control* registers of the JTAG UART. As we said in Section 2.10, *RAVAIL* in the *Data* register gives the number of characters that are stored in the receive FIFO, and *WSPACE* gives the amount of unused space that is available in the transmit FIFO. The *RE* and *WE* bits in Figure 16 are used to enable processor interrupts associated with the receive and transmit FIFOs. When enabled, interrupts are generated when *RAVAIL* for the receive FIFO, or *WSPACE* for the transmit FIFO, exceeds 7. Pending interrupts are indicated in the Control register's *RI* and *WI* bits, and can be cleared by writing or reading data to/from the JTAG UART.

Figure 16. Interrupt bits in the JTAG UART registers.

#### 3.6 Using Interrupts with Assembly Language Code

An example of assembly language code for the DE1-SoC Computer that uses interrupts is shown in Listing 7, which has three main parts. The beginning part of the code sets up the exception vector table. This code must be in a special

assembler section called .section, as shown. The entries in the table provide branches to the various exception service routines; they are discussed later in this section.

When this code is executed on the DE1-SoC board it displays a rotating pattern on the LEDs. The pattern's rotation can be toggled through pressing the pushbutton KEYs. Different types of interrupts are used in the code. The LEDs are controlled by interrupts from the FPGA interval timer, and the KEYs are also handled through interrupts.

The main program initializes the A9 banked stack pointer (sp) registers for interrupt (IRQ) mode and supervisor (SVC) mode, because these are the processor modes that are used in the program. The code then calls subroutines to initialize the HPS timer, FPGA interval timer, and FPGA pushbutton KEYs. Finally, the code initializes the HPS GPIO1 port, enables IRQ interrupts in the A9 processor, and then enters an infinite loop. The loop code turns on and off a green light whenever the global variable named *tick* is set to 1. This variable is set to 1 by the exception service routine for the HPS timer, which is described later in this section.

Following are the subroutines used to initialize the timers and pushbutton KEYs. The CONFIG\_HPS\_TIMER routine sets up the HPS timer 0 so that it will produce an interrupt every one second. Since this timer uses a 100 MHz clock, the timer *load* register is initialized to the value  $100 \times 10^6$ . The CONFIG\_INTERVAL\_TIMER routine configures the FPGA interval timer to produce interrupts every 50 msec. Since this timer uses a 100 MHz clock, the required starting count value is  $5 \times 10^6$ . The CONFIG\_KEYS routine sets up the FPGA KEYs parallel port to produce an interrupt when any KEY is pressed.

The last portion of the code shows the global data used by the program. It includes the *tick* variable that was discussed for the code earlier, and other variables. The *pattern* variable holds the bit-pattern that is written, the *key\_pressed* variable indicates which FPGA KEY has been recently pressed, and the *shift\_dir* variable specifies the direction of shifting for the HEX displays.

Also included in part c of Listing 7 is the subroutine that initializes the GIC. This code performs the minimum-required steps needed to configure the three interrupts used in the program, by writing to the *processor targets* (ICDIPTRn) registers in the GIC, and the *set enable* (ICDISERn) registers. For the HPS timer, the registers used have addresses 0xFFFED8C4 and 0xFFFED118, as shown in the listing. For the FPGA interval timer and KEYs, the register addresses are 0xFFFED848 and 0xFFFED108. Instructions for calculating these addresses, and determining the bit patterns to write into them can be found in the tutorial *Using the Generic Interrupt Controller*, available in Intel's FPGA University Program website. The last part of the code in this section enables the CPU Interface and Distributor in the GIC.

The exception service routines for the main program in Listing 7 are given in Listing 8. The first part of the listing gives the IRQ exception handler. This routine first reads from the *interrupt acknowledge* register in the GIC to determine the interrupt ID of the peripheral that caused the interrupt. The code then checks which of the three possible sources of interrupt has occurred, and calls the corresponding interrupt service routine for the HPS timer, FPGA interval timer, or FPGA KEY parallel port. These interrupt service routine are shown in Listings 9 to 10.

Finally, the exception handler in Listing 8 writes to the *end-of-interrupt* register in the GIC to clear the interrupt, and then returns to the main program by using the instruction "SUBS PC, LR, #4".

The latter part of Listing 8 shows handlers for exceptions that correspond to the reset exception, various types of error conditions, and the FIQ interrupt. The reset handler shows a branch to the start of the main program in

Listing 7. This handler is just an indicator of the result of performing a reset of the A9 processor—the actual reset process involves executing code from a special boot ROM on the processor, and then executing a program called the *pre-loader* before actually starting the main program. More information about the reset process for the A9 processor can be found in the document "Using the Pre-loader Software for the A9 Processor," which is available from Intel's FPGA University Program website. The other handlers in the latter part of Listing 8, which are just loops that branch to themselves, are intended to serve as placeholders for code that would handle the corresponding exceptions. More information about each of these types of exceptions can be found in the document *Introduction to the ARM Processor*, also available in Intel's FPGA University Program web site.

### 3.7 Using Interrupts with C Code

An example of C code for the DE1-SoC Computer that uses interrupts is shown in Figure 12. This code performs exactly the same operations as the code described in Listing 7.

Before it call subroutines to configure the generic interrupt controller (GIC), timers, and pushbutton KEY port, the main program first initializes the IRQ mode stack pointer by calling the routine  $set\_A9\_IRQ\_stack()$ . The code for this routine uses in-line assembly language instructions, as shown in Part b of the listing. This step is necessary because the C compiler generates code to set only the supervisor mode stack, which is used for running the main program, but the compiler does not produce code for setting the IRQ mode stack. To enable IRQ interrupts in the A9 processor the main program uses the in-line assembly code shown in the subroutine called  $enable\_A9\_interrupts()$ .

The exception handlers for the main program in Listing 12 are given in Listing 13. These routines have unique names that are meaningful to the C compiler and linker tools, and they are declared with the special type of <u>\_\_attribute\_\_</u> called **interrupt**. These mechanisms cause the C compiler and linker to use the addresses of these routines as the contents of the exception vector table.

The function with the name \_\_cs3\_isr\_irq is the IRQ exception handler. As discussed for the assembly language code in Listing 8 this routine first reads from the *interrupt acknowledge* register in the GIC to determine the interrupt ID of the peripheral that caused the interrupt, and then calls the corresponding interrupt service routine for either the HPS timer, FPGA interval timer, or FPGA KEY parallel port. These interrupt service routines are shown in Listings 14 to 15.

Listing 13 also shows handlers for exceptions that correspond to the various types of error conditions and the FIQ interrupt. These handlers are just loops that are meant to serve as place-holders for code that would handle the corresponding exceptions.

The source code files shown in Listing 7 to Listing 16 are distributed as part of the Intel<sup>®</sup> FPGA Monitor Program. The files can be found under the heading *sample programs*, and are identified by the name *Interrupt Example*.

### 4 Media Components

This section describes the audio in/out, video-out, video-in, PS/2, IrDA\*, and ADC ports.

#### 4.1 Audio In/Out Port

The DE1-SoC Computer includes an audio port that is connected to the audio CODEC (COder/DECoder) chip on the DE1-SoC board. The default setting for the sample rate provided by the audio CODEC is 8K samples/sec. The audio port provides audio-input capability via the microphone jack on the DE1-SoC board, as well as audio output functionality via the line-out jack. The audio port includes four FIFOs that are used to hold incoming and outgoing data. Incoming data is stored in the left- and right-channel *Read* FIFOs, and outgoing data is held in the left- and right-channel *Write* FIFOs. All FIFOs have a maximum depth of 128 32-bit words.

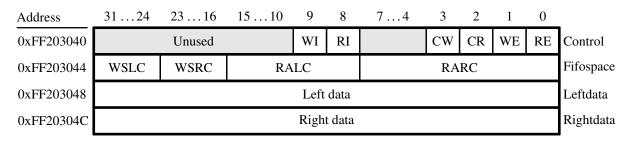

The audio port's programming interface consists of four 32-bit registers, as illustrated in Figure 17. The *Control* register, which has the address 0xFF203040, is readable to provide status information and writable to make control settings. Bit *RE* of this register provides an interrupt enable capability for incoming data. Setting this bit to 1 allows the audio core to generate a ARM A9 interrupt when either of the *Read* FIFOs are filled 75% or more. The bit *RI* will then be set to 1 to indicate that the interrupt is pending. The interrupt can be cleared by removing data from the *Read* FIFOs until both are less than 75% full. Bit *WE* gives an interrupt enable capability for outgoing data. Setting this bit to 1 allows the audio core to generate an interrupt when either of the *Write* FIFOs are less that 25% full. The bit *WI* will be set to 1 to indicate that the interrupt is pending, and it can be cleared by filling the *Write* FIFOs until both are more than 25% full. The bits *CR* and *CW* in Figure 17 can be set to 1 to clear the *Read* and *Write* FIFOs, respectively. The clear function remains active until the corresponding bit is set back to 0.

Figure 17. Audio port registers.

The read-only *Fifospace* register in Figure 17 contains four 8-bit fields. The fields RARC and RALC give the number of words currently stored in the right and left audio-input FIFOs, respectively. The fields WSRC and WSLC give the number of words currently available (that is, unused) for storing data in the right and left audio-out FIFOs. When all FIFOs in the audio port are cleared, the values provided in the Fifospace register are RARC = RALC = 0 and WSRC = WSLC = 128.

The *Leftdata* and *Rightdata* registers are readable for audio in, and writable for audio out. When data is read from these registers, it is provided from the head of the *Read* FIFOs, and when data is written into these registers it is loaded into the *Write* FIFOs.

A fragment of C code that uses the audio port is shown in Listing 17. The code checks to see when the depth of either the left or right *Read* FIFO has exceeded 75% full, and then moves the data from these FIFOs into a memory buffer. This code is part of a program that is distributed as part of the Intel® FPGA Monitor Program. The source code can be found under the heading sample programs, and is identified by the name Audio.

#### 4.2 Video-out Port

The DE1-SoC Computer includes a video-out port connected to the on-board VGA controller that can be connected to a standard VGA monitor. The video-out port support a screen resolution of  $640 \times 480$ . The image that is displayed by the video-out port is derived from two sources: a pixel buffer, and a character buffer.

#### 4.2.1 **Pixel Buffer**

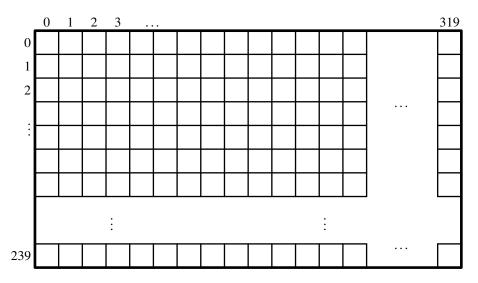

The pixel buffer for the video-out port holds the data (color) for each pixel that will be displayed. As illustrated in Figure 18, the pixel buffer provides an image resolution of 320 × 240 pixels, with the coordinate 0,0 being at the top-left corner of the image. Since the video-out port supports the screen resolution of 640 × 480, each of the pixel values in the pixel buffer is replicated in both the x and y dimensions when it is being displayed on the screen.

Figure 18. Pixel buffer coordinates.

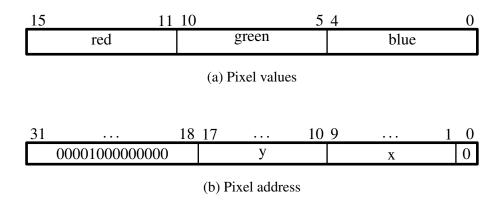

Figure 19a shows that each pixel color is represented as a 16-bit halfword, with five bits for the blue and red components, and six bits for green. As depicted in part b of Figure 19, pixels are addressed in the pixel buffer by using the combination of a base address and an x, y offset. In the DE1-SoC Computer the default address of the pixel buffer is 0xC8000000, which corresponds to the starting address of the FPGA on-chip memory. Using this scheme, = 0xC8000002, the pixel 0,1 has the address base +  $(00000001\ 000000000\ 0)_2$  = 0xC8000400, and the pixel at location 319,239 has the address  $base + (11101111 \ 100111111 \ 0)_2 = 0xC803BE7E$ .

You can create an image by writing color values into the pixel addresses as described above. A dedicated pixel buffer controller continuously reads this pixel data from sequential addresses in the corresponding memory for display on

Figure 19. Pixel values and addresses.

the screen. You can modify the pixel data at any time, simply by writing to the pixel addresses. Thus, an image can be changed even when it is in the process of being displayed. However, it is also possible to avoid making changes to the pixel buffer while it is being displayed, by using the concept of *double-buffering*. In this scheme, two pixel buffers are involved, called the *front* and *back* buffers, described below.

#### 4.2.2 RGB Resampling

The DE1-SoC Computer contains an RGB Resampler for converting video streams between RGB color formats. Reading from the 32-bit *Status* register at address 0xFF203010 provides information about alpha/no alpha, color/grayscale, and mode for the incoming and outgoing formats. The incoming format for the DE1-SoC Computer video stream is 0x14, which corresponds to no alpha, color, 16-bit RGB (5-bit Red, 6-bit Green, 5-bit Blue). For more information, the reader should refer to the video module's online documentation, *Video IP Cores for Intel DE-Series Boards*, which is available from Intel's FPGA University Program web site.

#### 4.2.3 Double Buffering

As mentioned above, a pixel buffer controller reads data out of the pixel buffer so that it can be displayed on the screen. This pixel buffer controller includes a programming interface in the form of a set of registers, as illustrated in Table 2. The register at address 0xFF203020 is called the *Buffer* register, and the register at address 0xFF203024 is the *Backbuffer* register. Each of these registers stores the starting address of a pixel buffer. The Buffer register holds the address of the pixel buffer that is displayed on the screen. As mentioned above, in the default configuration of the DE1-SoC Computer this Buffer register is set to the address 0xC8000000, which points to the start of the FPGA on-chip memory. The default value of the Backbuffer register is also 0xC8000000, which means that there is only one pixel buffer. But software can modify the address stored in the Backbuffer register, thereby creating a second pixel buffer. The pixel buffer can be located in the SDRAM memory in the DE1-SoC Computer, which has the base address 0xC0000000. Note that the pixel buffer cannot be located in the DDR3 memory in the DE1-SoC Computer, because the pixel buffer controller is not connected to the DDR3 memory. An image can be drawn into the second buffer by writing to its pixel addresses. This image is not displayed on the screen until a pixel buffer *swap* is performed, as explained below.

A pixel buffer swap is caused by writing the value 1 to the Buffer register. This write operation does not directly modify the content of the Buffer register, but instead causes the contents of the Buffer and Backbuffer registers to be swapped. The swap operation does not happen right away; it occurs at the end of a screen-drawing cycle, after the last pixel in the bottom-right corner has been displayed. This time instance is referred to as the *vertical synchronization* time, and occurs every 1/60 seconds. Software can poll the value of the S bit in the Status register, at address 0xFF20302C, to see when the vertical synchronization has happened. Writing the value 1 into the Buffer register causes S to be set to 1. Then, when the swap of the Buffer and Backbuffer registers has been completed S is reset back to 0.

| Address     | Register   | R/W Bit Description |                             |      |      |     |    |     |    |   |   |

|-------------|------------|---------------------|-----------------------------|------|------|-----|----|-----|----|---|---|

|             | Name       | IX/ VV              | 3124                        | 2316 | 1512 | 118 | 76 | 53  | 2  | 1 | 0 |

| 0xFF203020  | Buffer     | R                   | Buffer's start address      |      |      |     |    |     |    |   |   |

| 0xFF203024  | BackBuffer | R/W                 | Back buffer's start address |      |      |     |    |     |    |   |   |

| 0xFF203028  | Resolution | R                   | 7                           | Y    |      | X   |    |     |    |   |   |

| 0xFF20302C  | Status     | R                   | m                           | n    | (1)  | BS  | SB | (1) | EN | A | S |

| 0X11120302C | Control    | W                   | EN   (1)                    |      |      |     | ') |     |    |   |   |

#### Notes:

(1) Reserved. Read values are undefined. Write zero.

Table 2. Pixel Buffer Controller

In a typical application the pixel buffer controller is used as follows. While the image contained in the pixel buffer that is pointed to by the Buffer register is being displayed, a new image is drawn into the pixel buffer pointed to by the Backbuffer register. When this new image is ready to be displayed, a pixel buffer swap is performed. Then, the pixel buffer that is now pointed to by the Backbuffer register, which was already displayed, is cleared and the next new image is drawn. In this way, the next image to be displayed is always drawn in the "back" pixel buffer, and the two pixel buffer pointers are swapped when the new image is ready to be displayed. Each time a swap is performed software has to synchronize with the video-out port by waiting until the S bit in the Status register becomes 0.

As shown in Table 2 the *Status* register contains additional information other than the *S* bit. The fields *n* and *m* give the number of address bits used for the *X* and *Y* pixel coordinates, respectively. The *BS* field specifies the number of data bits per symbol minus one. The *SB* field specifies the number of symbols per beat minus one. The *A* field allows the selection of two different ways of forming pixel addresses. If configured with A = 0, then the pixel controller expects addresses to contain *X* and *Y* fields, as we have used in this section. But if A = 1, then the controller expects addresses to be consecutive values starting from 0 and ending at the total number of pixels–1. The *EN* field is used to enable or disable the DMA controller. If this bit is set to 0, the DMA controller will be turned off.

In Table 2 the default values of the status register fields in the DE1-SoC Computer are used when forming pixel addresses. The defaults are n = 9, m = 8, and A = 0. If the pixel buffer controller is changed to provide different values of these fields, then the way in which pixel addresses are formed has to be modified accordingly. The programming interface also includes a *Resolution* register, shown in Table 2, that contains the X and Y resolution of the pixel buffer(s).

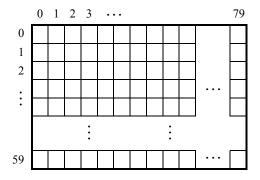

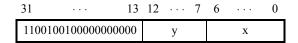

#### 4.2.4 Character Buffer

The character buffer for the video-out port is stored in on-chip memory in the FPGA on the DE1-SoC board. As illustrated in Figure 20a, the buffer provides a resolution of 80 × 60 characters, where each character occupies an 8 × 8 block of pixels on the screen. Characters are stored in each of the locations shown in Figure 20a using their ASCII codes; when these character codes are displayed on the monitor, the character buffer automatically generates the corresponding pattern of pixels for each character using a built-in font. Part b of Figure 20 shows that characters are addressed in the memory by using the combination of a base address, which has the value 0xC9000000, and an x, y offset. Using this scheme, the character at location 0,0 has the address 0xC9000000, the character 1,0 has the address base + (000000 0000001) $_2$  = 0xC9000001, the character 0,1 has the address base + (000001 00000000) $_2$  = 0xC9000080, and the character at location 79,59 has the address base + (111011 1001111) $_2$  = 0xC9001DCF.

(a) Character buffer coordinates

(b) Character buffer addresses

Figure 20. Character buffer coordinates and addresses.

#### 4.2.5 Using the Video-out Port with C code

A fragment of C code that uses the pixel and character buffers is shown in Listing 18. The first **for** loop in the figure draws a rectangle in the pixel buffer using the color  $pixel\_color$ . The rectangle is drawn using the coordinates  $x_1, y_1$  and  $x_2, y_2$ . The second **while** loop in the figure writes a null-terminated character string pointed to by the variable  $text\_ptr$  into the character buffer at the coordinates x, y. The code in Listing 18 is included in the sample program called *Video* that is distributed with the Intel<sup>®</sup> FPGA Monitor Program.

#### 4.3 Video-in Port

The DE1-SoC Computer includes a video-in port for use with the composite video-in connector on the DE1-SoC board. The video analog-to-digital converter (ADC) connected to this port is configured to support an NTSC

video source. The video-in port provides frames of video at a resolution of 320 x 240 pixels. These video frames can be displayed on a monitor by using the video-out port described in Section 4.2. The video-in port writes each frame of the video-in data into the pixel buffer described in Section 4.2.1. The video-in port can be configured to provide two types of images: either the "raw" image provided by the video ADC, or a version of this image in which only "edges" that are detected in the image are drawn.

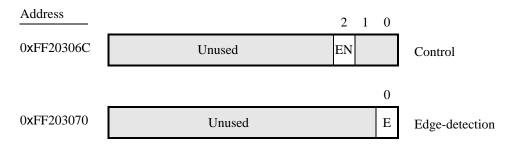

The video-in port has a programming interface that consists of two registers, as illustrated in Figure 21. The *Control* register at the address 0xFF20306C is used to enable or disable the video input. If the *EN* bit in this register is set to 0, then the video-in core does not store any data into the pixel buffer. Setting *EN* to 1 and then changing *EN* to 0 can be used to capture a still picture from the video-in port.

The register at address 0xFF203070 is used to enable or disable edge detection. Setting the E bit in this register to 1 causes the input video to passed through hardware circuits that detect edges in the images. The image stored in the pixel buffer will then consist of dark areas that are puctuated by lighter lines along the edges that have been detected. Setting E = 0 causes a normal image to be stored into the pixel buffer.

Figure 21. The video-in port programming interface.

#### 4.3.1 DMA Controller for Video

The data provided by the Video-In core is stored into memory using a DMA Controller for Video. When operating in *Stream to Memory* mode, the DMA stores the incoming frames to memory. Table 3 describes the registers used in the DMA Controller.

| Address     | Register   | R/W Bit Description |                             |      |      |     |    |     |    |   |   |

|-------------|------------|---------------------|-----------------------------|------|------|-----|----|-----|----|---|---|

|             | Name       | K/W                 | 3124                        | 2316 | 1512 | 118 | 76 | 53  | 2  | 1 | 0 |

| 0xFF203060  | Buffer     | R                   | Buffer's start address      |      |      |     |    |     |    |   |   |

| 0xFF203064  | BackBuffer | R/W                 | Back buffer's start address |      |      |     |    |     |    |   |   |

| 0xFF203068  | Resolution | R                   | Y                           |      | X    |     |    |     |    |   |   |

| 0xFF20306C  | Status     | R                   | m                           | n    | (1)  | BS  | SB | (1) | EN | A | S |

| 0x11120300C | Control    | W                   | (1) EN                      |      |      | (1  | () |     |    |   |   |

#### Notes:

(1) Reserved. Read values are undefined. Write zero.

Table 3. Video DMA Controller

The incoming video is stored to memory, starting at the address specified in the *Buffer* register. The *BackBuffer* register is used to store an alternate memory location. To change where the video is stored, the new location should first be written into the *BackBuffer*. Then the value in the *BackBuffer* and *Buffer* registers can be switched by performing a write to the *Buffer* register.

Bit 2 of the *Status/Control* register, *EN*, is used to enable or disable the Video DMA controller. In the DE1-SoC Computer, the DMA controller is disabled by default. To enable the DMA controller, write a 1 into this location. The Video DMA Controller will then begin storing the video into the location specified in the *Buffer* register.

The default value stored in the *Buffer* register is 0x08000000. This address is also used as the source for the Video-Out port, as described in Section 4.2, allowing the Video In stream to be displayed on the VGA. If the Video-Out is intended to display a different signal, than the address stored in the Video DMA Controller's *Buffer* register should be changed.

#### 4.4 Audio/Video Configuration Module

The audio/video configuration module controls settings that affect the operation of both the audio port and the videoout port. The audio/video configuration module automatically configures and initializes both of these ports whenever the DE1-SoC Computer is reset. For typical use of the DE1-SoC Computer it is not necessary to modify any of these default settings. In the case that changes to these settings are needed, the reader should refer to the audio/video configuration module's online documentation, which is available from Intel's FPGA University Program web site.

#### 4.5 **PS/2 Port**

The DE1-SoC Computer includes two PS/2 ports that can be connected to a standard PS/2 keyboard or mouse. The port includes a 256-byte FIFO that stores data received from a PS/2 device. The programming interface for the PS/2 port consists of two registers, as illustrated in Figure 22. The *PS2\_Data* register is both readable and writable. When bit 15, *RVALID*, is 1, reading from this register provides the data at the head of the FIFO in the *Data* field, and the number of entries in the FIFO (including this read) in the *RAVAIL* field. When *RVALID* is 1, reading from the *PS2\_Data* register decrements this field by 1. Writing to the *PS2\_Data* register can be used to send a command in the *Data* field to the PS/2 device.

The  $PS2\_Control$  register can be used to enable interrupts from the PS/2 port by setting the RE field to the value 1. When this field is set, then the PS/2 port generates an interrupt when RAVAIL > 0. While the interrupt is pending the field RI will be set to 1, and it can be cleared by emptying the PS/2 port FIFO. The CE field in the  $PS2\_Control$  register is used to indicate that an error occurred when sending a command to a PS/2 device.

Figure 22. PS/2 port registers.

A fragment of C code that uses the PS/2 port is given in Listing 19. This code reads the content of the *Data* register, and saves data when it is available. If the code is used continually in a loop, then it stores the last three bytes of data received from the PS/2 port in the variables  $byte_1$ ,  $byte_2$ , and  $byte_3$ . This code is included as part of a sample program called *PS2* that is distributed with the Intel<sup>®</sup> FPGA Monitor Program.

#### 4.5.1 PS/2 Port Dual

The DE1-SoC Computer includes a second PS/2 port that allows both a keyboard and mouse to be used at the same time. To use the dual port a Y-splitter cable must be used and the keyboard and mouse must be connected to the PS/2 connector on the DE1-SoC board through this cable. The PS/2 port dual has the same registers as the PS/2 port shown in Listing 19, except that the base address of its *PS2\_Data* register is 0xFF200108 and the base address of its *PS2\_Control* register is 0xFF20010C.

#### 4.6 IrDA\* Port

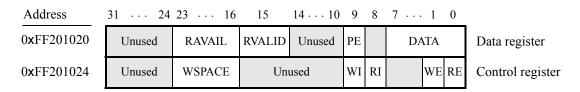

The DE1-SoC Computer includes an IrDA UART for communicating wirelessly with peripherals over the infrared spectrum. It is configured for 8-bit data and one stop bit, and operates at a baud rate of 155,200. The default configuration does not use a parity bit. The programming interface consists of two 32-bit registers, as shown in Figure 23. The register at address 0xFF201020 is referred to as the *Data* register, and the register at address 0xFF201024 is the *Control* register.

The operation of the IrDA UART is similar to the Serial Port UART described above. Data recieved through the IrDA is stored in a 128-character FIFO in the UART. As shown in Figure 23, the number of characters, *RAVAIL*, currently stored in this FIFO is provided in bits 23–16 of the *Data* register. If the FIFO overflows, then any additional data is lost. When a read of the *Data* register is performed, the character at the head of the FIFO is provided in bits 7–0. If the character read is valid, the the value of bit 15, *RVALID* will be one. If no data is available to be read from the receive FIFO, then *RVALID* will be set to 0 and the data in bits 7–0 is undefined.

Figure 23. IrDA UART registers.

The *Control* register bits *RE* and *RI* are described in section 3.

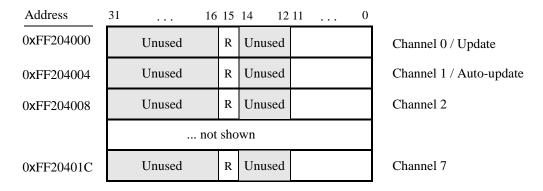

### 4.7 Analog-to-Digital Conversion Port

The Analog-to-Digital Conversion (ADC) Port provides access to the eight-channel, 12-bit analog-to-digital converter on the DE1-SoC board. As illustrated in Figure 24, the ADC port comprises eight 12-bit registers starting at the base address 0xFF204000. The first two registers have dual purposes, acting as both data and control registers. By default, the ADC port updates the A-to-D conversion results for all ports only when instructed to do so. Writing to the control register at address 0xFF204000 causes this update to occur. Reading from the register at address

0xFF204000 provides the conversion data for channel 0. Reading from the other seven registers provides the conversion data for the corresponding channels. It is also possible to have the ADC port continually request A-to-D conversion data for all channels. This is done by writing the value 1 to the control register at address 0xFF204004. The *R* bit of each channel register in Figure 24 is used in Auto-update mode. *R* is set to 1 when its corresponding channel is refreshed and set to 0 when the channel is read.

Figure 24. ADC port registers.

Figure 25 shows the connector on the DE1-SoC board that is used with the ADC port. Analog signals in the range of 0 V to the  $V_{CC5}$  power-supply voltage can be connected to the pins for channels 0 to 7.

Figure 25. ADC connector.

### 5 Modifying the DE1-SoC Computer

It is possible to modify the DE1-SoC Computer by using Intel's Quartus<sup>®</sup> Prime software and Qsys tool. Tutorials that introduce this software are provided in the University Program section of Intel's web site. To modify the system it is first necessary to make an editable copy of the DE1-SoC Computer. The files for this system are installed as part of the Monitor Program installation. Locate these files, copy them to a working directory, and then use the Quartus Prime and Qsys software to make any desired changes.

Table 4 lists the names of the Qsys IP cores that are used in this system. When the DE1-SoC Computer design files are opened in the Quartus Prime software, these cores can be examined using the Qsys System Integration tool. Each core has a number of settings that are selectable in the Qsys System Integration tool, and includes a datasheet that provides detailed documentation.

The steps needed to modify the system are:

- 1. Install the *University Program IP Cores* from Intel's FPGA University Program web site

- 2. Copy the design source files for the DE1-SoC Computer from the University Program web site. These files can be found in the *Design Examples* section of the web site

- 3. Open the DE1-SoC\_Computer.qpf project in the Quartus Prime software

- 4. Open the Qsys System Integration tool in the Quartus Prime software, and modify the system as desired

- 5. Generate the modified system by using the Qsys System Integration tool

- 6. It may be necessary to modify the Verilog or VHDL code in the top-level module, DE1-SoC\_Computer.v/vhd, if any I/O peripherals have been added or removed from the system

- 7. Compile the project in the Quartus Prime software

- 8. Download the modified system into the DE1-SoC board

The DE1-SoC Computer includes a Nios II/f processor. When using the Quartus Prime Web Edition, compiling a design with a Nios II/s or Nios II/f processor will produce a time-limited SOF file. As a result, the board must remain connected to the host computer, and the design cannot be set as the default configuration, as discussed in Section 6. Designs using only Nios II/e processors and designs compiled using the Quartus Prime Subscription Edition do not have this restriction.

### 6 Making the System the Default Configuration

The DE1-SoC Computer can be loaded into the nonvolatile FPGA configuration memory on the DE1-SoC board, so that it becomes the default system whenever the board is powered on. Instructions for configuring the DE1-SoC board in this manner can be found in the tutorial *Introduction to the Quartus Prime Software*, which is available from Intel's FPGA University Program.

| I/O Peripheral                   | <b>Qsys Core</b>                 |

|----------------------------------|----------------------------------|

| SDRAM                            | SDRAM Controller                 |

| SRAM                             | SRAM Controller                  |

| On-chip memory character buffer  | Character Buffer for VGA Display |

| SD Card                          | SD Card Interface                |

| Flash                            | Intel UP Flash Memory IP Core    |

| Red LED parallel port            | Parallel Port                    |

| 7-segment displays parallel port | Parallel Port                    |

| Expansion parallel ports         | Parallel Port                    |

| Slider switch parallel port      | Parallel Port                    |

| Pushbutton parallel port         | Parallel Port                    |

| PS/2 port                        | PS2 Controller                   |

| JTAG port                        | JTAG UART                        |

| Serial port                      | RS232 UART                       |

| IrDA port                        | IrDA UART                        |

| Interval timer                   | Interval timer                   |

| System ID                        | System ID Peripheral             |

| Audio/video configuration port   | Audio and Video Config           |

| Audio port                       | Audio                            |

| Video port                       | Pixel Buffer DMA Controller      |

| Video In port                    | DMA Controller                   |

Table 4. Qsys cores used in the DE1-SoC Computer.

## 7 Memory Layout

Table 5 summarizes the memory map used in the DE1-SoC Computer.

| Base Address | End Address | I/O Peripheral                       |

|--------------|-------------|--------------------------------------|

| 0x00000000   | 0x3FFFFFFF  | DDR3 Memory                          |

| 0xFFFF0000   | 0xFFFFFFFF  | A9 On-chip Memory                    |

| 0xC0000000   | 0xC3FFFFFF  | SDRAM                                |

| 0xC8000000   | 0xC803FFFF  | FPGA On-chip Memory                  |

| 0xC9000000   | 0xC9001FFF  | FPGA On-chip Memory Character Buffer |

| 0xFF200000   | 0xFF20000F  | Red LEDs                             |

| 0xFF200020   | 0xFF20002F  | 7-segment HEX3-HEX0 Displays         |

| 0xFF200030   | 0xFF20003F  | 7-segment HEX5-HEX4 Displays         |

| 0xFF200040   | 0xFF20004F  | Slider Switches                      |

| 0xFF200050   | 0xFF20005F  | Pushbutton KEYs                      |

| 0xFF200060   | 0xFF20006F  | JP1 Expansion                        |

| 0xFF200070   | 0xFF20007F  | JP2 Expansion                        |

| 0xFF200100   | 0xFF200107  | PS/2                                 |

| 0xFF200108   | 0xFF20010F  | PS/2 Dual                            |

| 0xFF201000   | 0xFF201007  | JTAG UART                            |

| 0xFF201008   | 0xFF20100F  | Second JTAG UART                     |

| 0xFF201020   | 0xFF201027  | Infrared (IrDA)                      |

| 0xFF202000   | 0xFF20201F  | Interval Timer                       |

| 0xFF202020   | 0xFF20202F  | Second Interval Timer                |

| 0xFF203000   | 0xFF20301F  | Audio/video Configuration            |

| 0xFF203020   | 0xFF20302F  | Pixel Buffer Control                 |

| 0xFF203030   | 0xFF203037  | Character Buffer Control             |

| 0xFF203040   | 0xFF20304F  | Audio                                |

| 0xFF203060   | 0xFF203070  | Video-in                             |

| 0xFF204000   | 0xFF20401F  | ADC                                  |

| 0xFF709000   | 0xFF709063  | HPS GPIO1                            |

| 0xFFC04000   | 0xFFC040FC  | HPS I2C0                             |

| 0xFFC08000   | 0xFFC08013  | HPS Timer0                           |

| 0xFFC09000   | 0xFFC09013  | HPS Timer1                           |

| 0xFFD00000   | 0xFFD00013  | HPS Timer2                           |

| 0xFFD01000   | 0xFFD01013  | HPS Timer3                           |

| 0xFFD0501C   | 0xFFD0501F  | FPGA Bridge                          |

| 0xFFFEC100   | 0xFFFEC1FC  | GIC CPU Interface                    |

| 0xFFFED000   | 0xFFFEDFFC  | GIC Distributor Interface            |

| 0xFFFEC600   | 0xFFFEC60F  | ARM A9 Private Timer                 |

Table 5. Memory layout used in the DE1-SoC Computer.

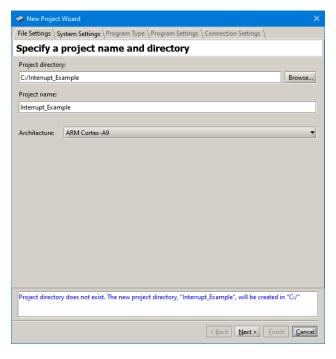

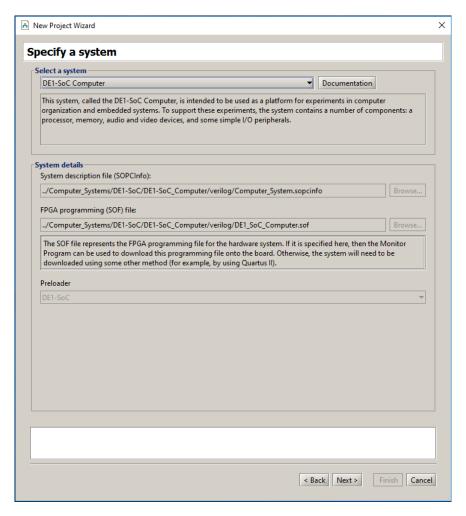

# 8 Intel<sup>®</sup> FPGA Monitor Program Integration

As we mentioned earlier, the DE1-SoC Computer system, and the sample programs described in this document, are made available as part of the Intel® FPGA Monitor Program. Figures 26 to 29 show a series of windows that are used in the Monitor Program to create a new project. In the first screen, shown in Figure 26, the user specifies a file system folder where the project will be stored, gives the project a name, and specifies the type of processor that is being used. Pressing Next opens the window in Figure 27. Here, the user can select the DE1-SoC Computer as a pre-designed system. The Monitor Program then fills in the relevant information in the *System details* box, which includes the appropriate system info and fpga configuration files, and preloader. The first of these files specifies to the Monitor Program information about the components that are available in the DE1-SoC Computer, such as the type of processor and memory components, and the address map. The second file is an FPGA programming bitstream for the DE1-SoC Computer, which can downloaded by the Monitor Program into the DE1-SoC board. Any system which contains a Hard Processor System (HPS) component must also specify the preloader to be run immediately following the circuit being downloaded. This preloader is used to configure the components within the HPS with the setting required for the specific board.

Figure 26. Specifying the project folder and project name.

Pressing Next again opens the window in Figure 28. Here the user selects the type of program that will be used, such as Assembly language, or C. Then, the check box shown in the figure can be used to display the list of sample programs for the DE1-SoC Computer that are described in this document. When a sample program is selected in this list, its source files, and other settings, can be copied into the project folder in subsequent screens of the Monitor Program.

Figure 29 gives the final screen that is used to create a new project in the Monitor Program. This screen shows the default addresses of compiler and linker sections that will be used for the assembly language or C program associated with the Monitor Program project. In the figure, the drop-down menu called *Linker Section Presets* has been set to Exceptions. With this setting the Monitor Program uses specific compiler and linker sections for the selected processor. For the Nios II processor, these sections are for reset and exceptions code, and another section for the main program, called *.text*. For the A9 processor, it has a section for the exception table, called *.vectors*, and another section for the main program, called *.text*. It also shows the initial value used to set the main stack pointer for C programs, which is the starting address of the *.stack* section.

Figure 27. Specifying the DE1-SoC Computer system.

Figure 28. Selecting sample programs.

Figure 29. Setting offsets for .text and .data.

### 9 Appendix

This section contains all of the source code files mentioned in the document.

#### 9.1 Timers

.end

```

"address map arm.s"

.include

.equ

bit 24 pattern, 0x01000000

/* This program provides a simple example of code for the ARM A9. The program

* performs the following:

* 1. starts the ARM A9 private timer

* 2. loops forever, toggling the HPS green light LEDG when the timer expires

.text

.global

_start

_start:

LDR

RO, =HPS_GPIO1_BASE // GPIO1 base address

R1, =MPCORE_PRIV_TIMER // MPCore private timer base address

LDR

R2, =bit_24_pattern

// value to turn on the HPS green light LEDG

LDR

STR

R2, [R0, #0x4]

// write to the data direction register to

// set bit 24 (LEDG) of GPI01 to be an

output

R3, =200000000

LDR

// timeout = 1/(200 MHz) \times 200 \times 10^6 = 1 sec

R3, [R1]

// write to timer load register

STR

R3, #0b011

// set bits: mode = 1 (auto), enable = 1

MOV

R3, [R1, #0x8]

// write to timer control register

STR

LOOP:

R2, [R0]

STR

// turn on/off LEDG

WAIT:

R3, [R1, #0xC]

// read timer status

LDR

CMP

R3, #0

WAIT

BEQ

// wait for timer to expire

R3, [R1, #0xC]

// reset timer flag bit

STR

EOR

R2, R2, #bit 24 pattern // toggle LEDG value

LOOP

```

Listing 1. An example of assembly language code that uses a timer.

```

#include "address_map_arm.h"

#define bit_24_pattern 0x01000000

/* This program provides a simple example of code for the ARM A9. The

* program performs the following:

* 1. starts the ARM A9 private timer

2. loops indefinitely, toggling the green light LEDG when the timer expires

int main(void)

/* Declare volatile pointers to I/O registers (volatile means that the

* locations will not be cached, even in registers) */

volatile int * HPS_GPI01_ptr = (int *)HPS_GPI01_BASE;

volatile int * MPcore_private_timer_ptr = (int *)MPCORE_PRIV_TIMER;

int HPS_LEDG = bit_24_pattern; // value to turn on the HPS green light LEDG

*(HPS GPIO1 ptr + 1) =

bit_24_pattern; // write to the data direction register to set

// bit 24 (LEDG) of GPIO1 to be an output

*(MPcore_private_timer_ptr) = counter; // write to timer load register

*(MPcore_private_timer_ptr + 2) = 0b011; // mode = 1 (auto), enable = 1

while (1)

*HPS_GPIO1_ptr = HPS_LEDG; // turn on/off LEDG

while (*(MPcore_private_timer_ptr + 3) == 0)

// wait for timer to expire

;

*(MPcore_private_timer_ptr + 3) = 1; // reset timer flag bit

HPS_LEDG ^= bit_24_pattern; // toggle bit that controls LEDG

}

}

```

Listing 2. An example of C code that uses a timer.

#### 9.2 Parallel Ports

```

.include

"address_map_arm.s"

/**********************************

* This program demonstrates use of parallel ports in the Computer System

* It performs the following:

* 1. displays a rotating pattern on the LEDs

* 2. if a KEY is pressed, uses SW switches as the pattern

******************************

/* executable code follows */

.text

.global

_start

_start: